芯片是怎么实现多层堆叠的

*** 次数:1999998 已用完,请联系开发者***

唯特偶:国内有多家公司进行芯片堆叠技术研究和应用金融界6月16日消息,有投资者在互动平台向唯特偶提问:董秘好,请问目前国内芯片堆叠技术,是只有一家掌握吗?芯片堆叠对于公司产品需求变化如何?公司回答表示:尊敬的投资者,您好!目前国内有多家公司在进行芯片堆叠技术的研究和应用。公司一直重视产品技术创新,密切关注行业技术...

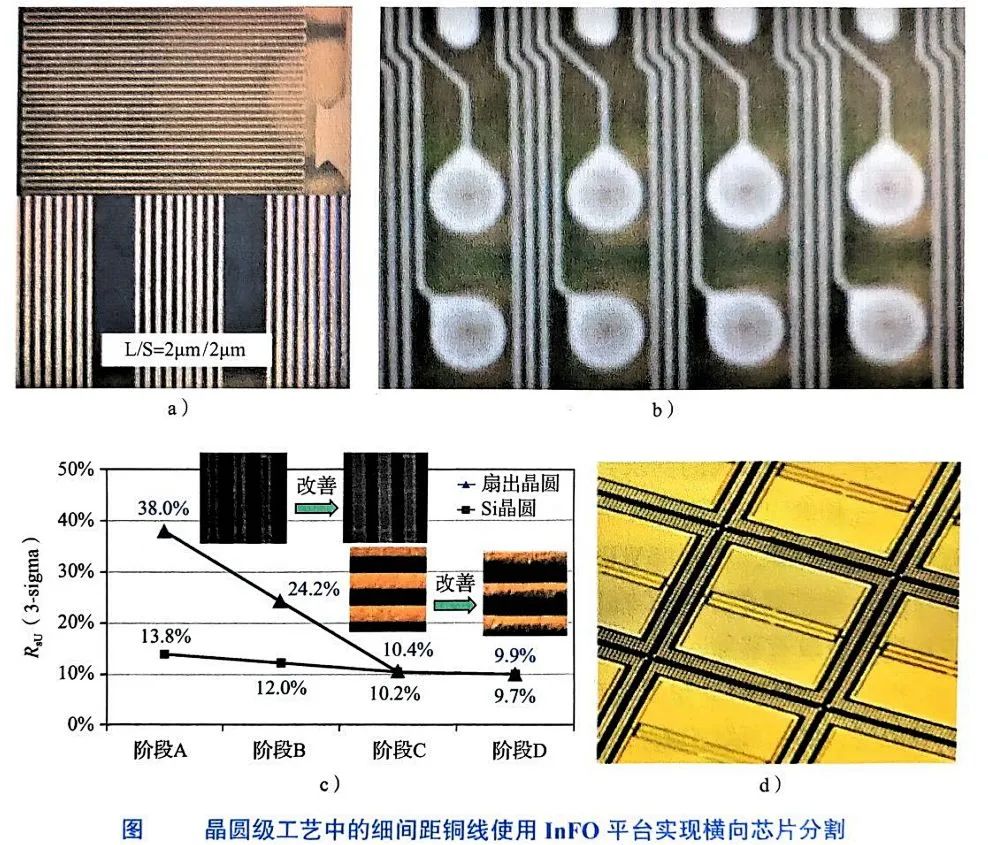

?0? 通富通科取得倒装芯片及多层堆叠芯片封装结构专利,提高芯片的可靠性金融界2024年10月17日消息,国家知识产权局信息显示,通富通科(南通)微电子有限公司取得一项名为“一种倒装芯片及多层堆叠芯片封装结构”的专利,授权公告号CN 221841838 U,申请日期为2024年2月。专利摘要显示,本公开实施例提供一种倒装芯片及多层堆叠芯片封装结构,该倒装...

+ω+

∩ω∩ 力积电:多层晶圆堆叠技术获AMD采用 开发3D AI芯片力积电今日宣布,旗下多层晶圆堆叠技术获AMD等大厂采用,结合晶圆代工大厂的先进逻辑制程,开发高频宽、高容量、低功耗的3D AI芯片。

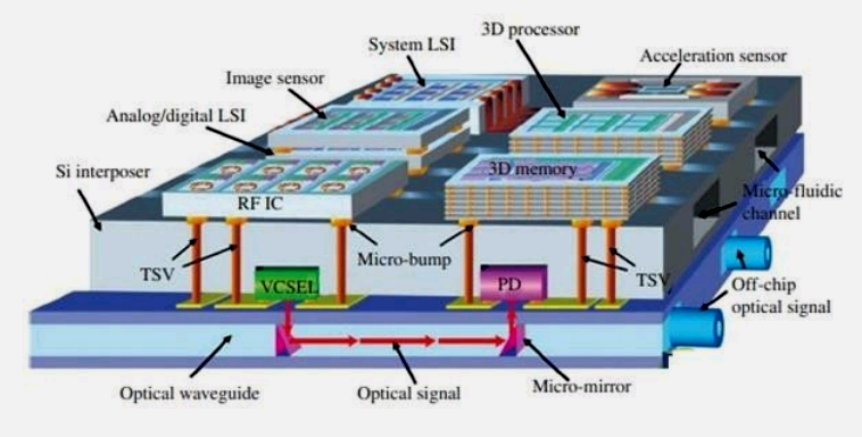

紫光国芯取得一种 3D 堆叠芯片专利,实现了 3D 堆叠集成逻辑芯片硬核 ...设置于基底层靠近硬核 IP 器件模块的一侧,硅通孔通过金属传输层形成的传输网络连接硬核 IP 器件模块。本实用新型通过硅通孔以及金属传输层形成的传输网络形成了先自下至上、再自上至下传输电和信号的方式,实现了 3D 堆叠集成逻辑芯片硬核 IP 器件模块的供电接入和信号接入。...

∪ω∪ 电子堆叠新技术造出多层芯片美国麻省理工学院团队在最新一期《自然》杂志上介绍了一种创新的电子堆叠技术。该技术能显著增加芯片上的晶体管数量,从而推动人工智能(AI)硬件发展更加高效。通过这种新方法,团队成功制造出了多层芯片,其中高质量半导体材料层交替生长,直接叠加在一起。

双K旗舰!红米这两款新机,猛得离谱Redmi K Pad将主板与核心芯片均置于机身中央。实现了芯片中置的堆叠重构,这种布局带来的直接好处便是改善了握持体验与散热效果。双电芯规格外加12050mm²超大铝合金液冷VC均热板,更是全面覆盖核心发热区,兼具高效导热与结构支撑。相比传统方案,K Pad的散热配置均热速...

紫光国芯取得一种存算一体的堆叠芯片专利,实现存储访问的高带宽、...金融界 2024 年 7 月 26 日消息,天眼查知识产权信息显示,西安紫光国芯半导体有限公司取得一项名为“一种存算一体的堆叠芯片“,授权公告号... 以将第一可编程门阵列组件、第二可编程门阵列组件以及第一存储阵列组件上的互连信号连接在一起。实现存储访问的高带宽、低功耗的目的...

...埋入式芯粒堆叠的封装结构、芯片封装方法专利,能够实现节省封装尺寸金融界2024年12月2日消息,国家知识产权局信息显示,新华三半导体技术有限公司申请一项名为“埋入式芯粒堆叠的封装结构、芯片封装方法”... 第二芯粒单元堆叠在晶圆载板之上,第二芯粒单元通过设置在表面的微金属凸块与晶圆载板的至少一个硅通孔电性连接。能够实现节省封装尺寸...

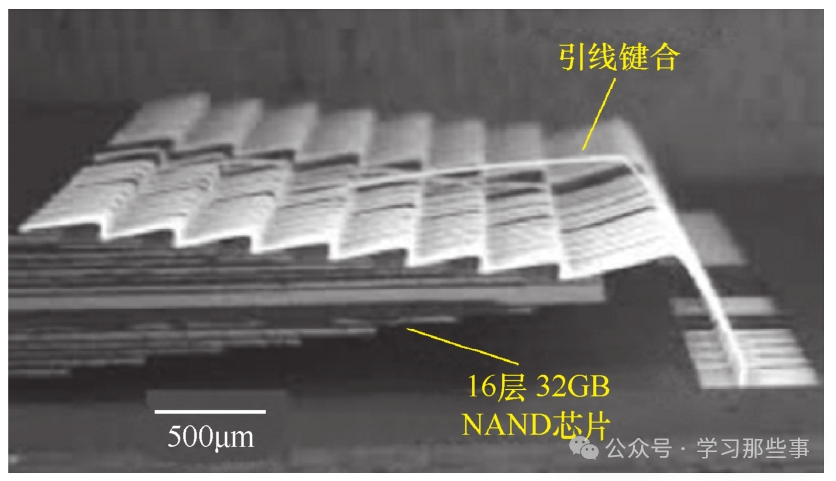

华天科技(南京)申请三维堆叠封装结构专利,实现芯片层数翻倍有限公司申请一项名为“一种三维堆叠封装结构”的专利,公开号CN 119050088 A,申请日期为2024年8月。专利摘要显示,本发明公开了一种三维堆叠封装结构,其通过把两块封装结构结合起来的思路实现芯片层数翻倍的效果,解决目前单独封装多层芯片遇到工艺瓶颈。其包括:上部基板...

江苏华创微系统取得倒装芯片与底层芯片的堆叠结构的制备方法专利金融界2024年9月26日消息,国家知识产权局信息显示,江苏华创微系统有限公司取得一项名为“倒装芯片与底层芯片的堆叠结构的制备方法”的专利,授权公告号CN 115410929 B,申请日期为2022年10月。

飞飞加速器部分文章、数据、图片来自互联网,一切版权均归源网站或源作者所有。

如果侵犯了你的权益请来信告知删除。邮箱:xxxxxxx@qq.com

上一篇:芯片是怎么实现多层堆叠的

下一篇:芒果NPV加速器